- 您现在的位置:买卖IC网 > Sheet目录3841 > PIC16C63A-04I/SO (Microchip Technology)IC MCU OTP 4KX14 PWM 28SOIC

134

SAM7S Series [DATASHEET]

6175M–ATARM–26-Oct-12

Power-off the chip

Power-on the chip with TST = 0

Assert Erase during a period of more than 220 ms

Power-off the chip

Then it is possible o return to FFPI mode and check that Flash is erased.

20.2.5.7

SAM7S512 Select EFC Command

The commands WPx, EA, xLB, xFB are executed using the current EFC controller. The default EFC controller is

EFC0. The Select EFC command (SEFC) allows selection of the current EFC controller.

20.2.5.8

Memory Write Command

This command is used to perform a write access to any memory location.

The Memory Write command (WRAM) is optimized for consecutive writes. Write handshaking can be chained; an

internal address buffer is automatically increased.

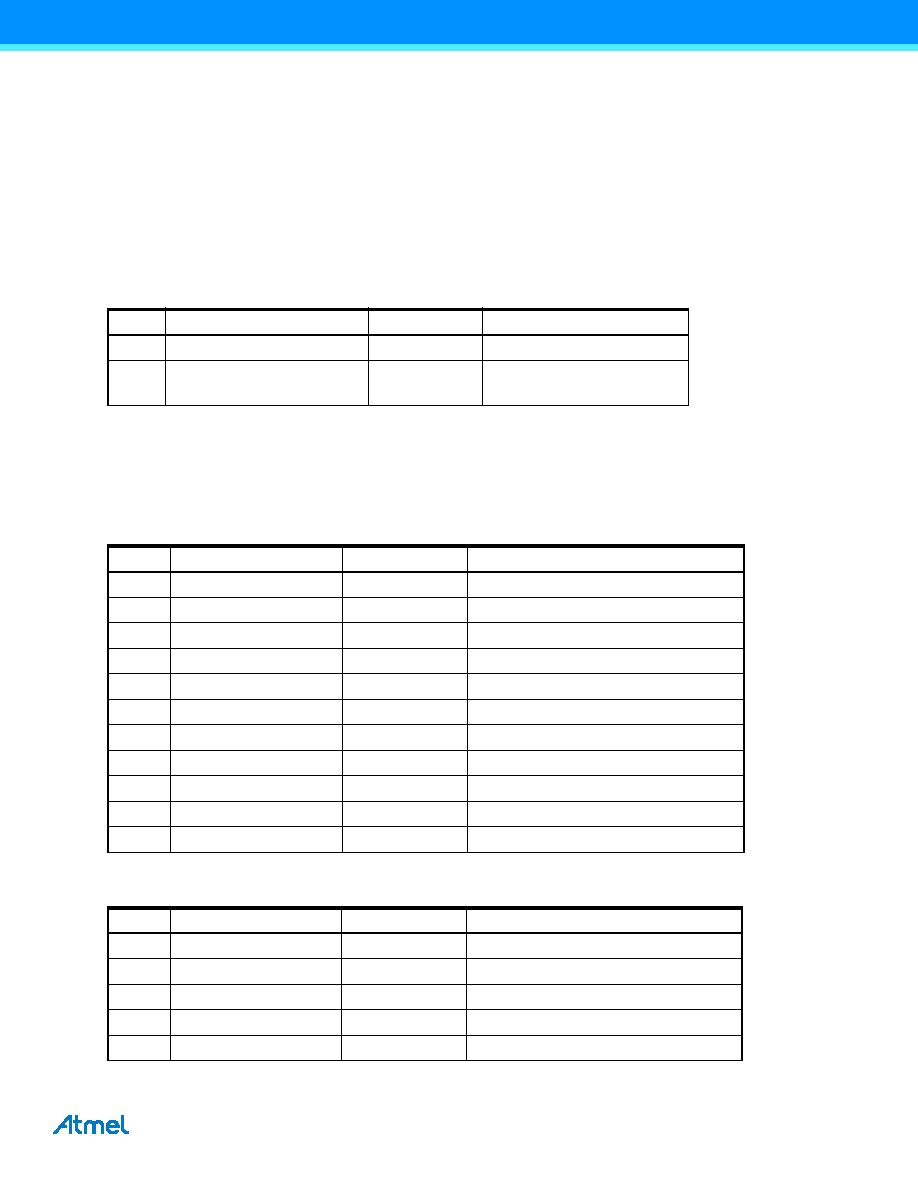

Table 20-16. Select EFC Command

Step

Handshake Sequence

MODE[3:0]

DATA[15:0]

1

Write handshaking

CMDE

SEFC

2

Write handshaking

DATA

0 = Select EFC0

1 = Select EFC1

Table 20-17. Write Command

Step

Handshake Sequence

MODE[3:0]

DATA[15:0]

1

Write handshaking

CMDE

WRAM

2

Write handshaking

ADDR0

Memory Address LSB

3

Write handshaking

ADDR1

Memory Address

4

Write handshaking

DATA

*Memory Address++

5

Write handshaking

DATA

*Memory Address++

...

n

Write handshaking

ADDR0

Memory Address LSB

n+1

Write handshaking

ADDR1

Memory Address

n+2

Write handshaking

DATA

*Memory Address++

n+3

Write handshaking

DATA

*Memory Address++

...

Table 20-18. Write Command

Step

Handshake Sequence

MODE[3:0]

DATA[7:0]

1

Write handshaking

CMDE

WRAM

2

Write handshaking

ADDR0

Memory Address LSB

3

Write handshaking

ADDR1

Memory Address

4

Write handshaking

ADDR2

Memory Address

5

Write handshaking

ADDR3

Memory Address

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

52559-2270

CONN FFC 22POS .5MM VERT ZIF SMD

52559-1870

CONN FFC 18POS .5MM VERT ZIF SMD

DSPIC33EP64MC506-I/PT

IC DSC 16BIT 64KB FLASH 64TQFP

52745-1896

CONN FFC 18POS .5MM R/A ZIF SMD

PIC16LC622-04/P

IC MCU OTP 2KX14 COMP 18DIP

PIC16LF84A-04/P

IC MCU FLASH 1KX14 EE 18DIP

DSPIC30F1010-30I/MM

IC DSPIC MCU/DSP 6K 28QFN

52745-1696

CONN FFC 16POS .5MM R/A ZIF SMD

相关代理商/技术参数

PIC16C63A-04I/SP

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A-04I/SS

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A04SP

制造商:MICROCHIP 功能描述:NEW

PIC16C63A-20/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A-20/SP

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A-20/SP

制造商:Microchip Technology Inc 功能描述:8 Bit Microcontroller Clock Speed:20MHz

PIC16C63A-20/SS

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A-20E/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT